| 您现在的位置:首页 > 技术资料 |

|

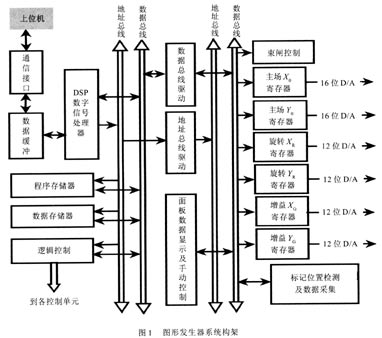

基于TMS320C6713的电子束曝光机图形发生器的硬件设计 摘要:提出了一套功能较为完备的新型扫描电子束曝光机图形发生器的硬件设计方案。方案采用 TMS320C6713芯片作为核心单元,并由USB2.0接口电路、存储器扩展电路、标记检测控制电路、曝光控制电路和束闸控制电路构成。方案具有数据处理能力强、速度快、接口方便等优势,克服了传统图形发生器单纯依靠软件完成、速度慢、精度低、工作不稳定的缺点。 关键词:电子束曝光机;图形发生器;数字信号处理 中图分类号:TN305.7 文献标识码:A 文章编号:1003-353X(2005)03-0054-04 1 引言 扫描电子束曝光系统是在20世纪60年代扫描电镜的基础上发展起来的,是微电子工业和微细加工研究领域首选大型精密设备。目前,新兴的纳米科技、MEMS、微光学、半导体前沿研究均需要纳米级曝光设备,在国防前沿领域中的特种高性能器件研究也依赖纳米级曝光设备。电子束缩小投影成像系统研究(第二阶段)――纳米级电子束曝光系统实用化是中国科学院知识创新工程重大项目。此实用化项目完成后将满足国内目前对纳米级光刻设备的要求。 图形发生器是电子束曝光系统中的一个关键部件。目前国内使用的图形发生器一般采用中小规模集成电路,存在图形运算速度慢、体积大、耗电大、效率低、工作极不稳定、单元图形种类少,故障多等缺点。随着数字信号处理技术的不断普及和应用,国外已经将数字信号处理器(DSP)作为图形发生器的核心单元开发了新的产品。国内在这方面的研究刚刚起步,虽然DSP在通讯工业和自动控制等领域中有所应用,但在电子束曝光系统中尚属前列。研究开发以DSP为核心的图形发生器具有现实意义和必要性。 2 图形发生器系统设计方案 新型图形发生器硬件方案如图1所示,主要由数字信号处理单元、接口单元、存储器扩展单元、逻辑控制单元、曝光控制单元、标记检测控制单元和束闸控制单元构成。该系统使用USB接口与上位机构建了高速的数据通路。DSP运算单元接收到上位机发送的单元图形数据后,按照预定的算法将其解析,得到各曝光点的数据。然后将曝光数据以并行方式送到高精度数模转换模块中,转换成模拟电压量,与DSP运算单元串行输送来的旋转( R)、增益(G)和位移(S)校正量求和后输出到适配器,使输出的电压值与偏转放大器匹配,驱动偏转放大器控制电子束偏转,对掩模或硅片进行扫描曝光。利用该系统的图像采集模块,可以对掩模或硅片的位置进行校准。

3 数字信号处理单元 DSP系统由于应用场所、应用目的等不尽相同,对DSP芯片的选择也是不同的。通常除了要考虑一般意义上的指标如功耗、性价比、开发周期和生存周期等,最主要的就是运算速度。本系统选用TI公司的通用型浮点DSP芯片TMS320C6713作为图形发生器的主控单元。 在本系统中每点曝光时间约为2μs,DSP工作在50MHz外部时钟源模式下,指令执行周期为40ns。因为DSP大多数指令仅需要一个周期,所以在2μs内可以执行50个指令,这对于一般的矩形和梯形生成而言是足够了。虽然对于圆及圆环等复杂图形涉及较多的乘法运算,而且处理数据量较大,但是因为DSP具有专用硬件乘法器,所以这个速度也是可以满足的。片外扩展一片16位的外部数据存储器,地址范围是CE0空间的8000 0000-8FFF FFFF。扩展一片外部FLASH ROM,地址范围是CE1空间的9000 0000-901F FFFF。接口部分占用CE1地址为9020 0000~9020 FFFF的空间。另外,接口电路还占用DSP一个外部中断管脚EXT- INT6作为中断申请。DSP系统上电引导方式采用16位异步外接ROM加载。加载的数据包格式为小终端方式,先读出低位地址的数据,将它们打包到EMIF数据接口最低有效字节,然后将后续的访问打包到高序的字节。

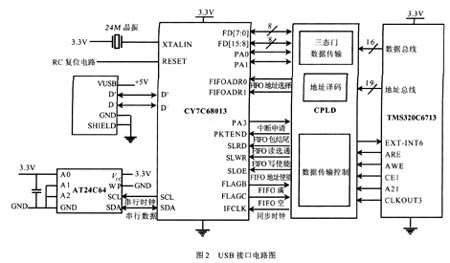

4 USB接口设计[2] DSP系统与上位机之间的通讯接口需要传送以下几种数据:(1)上位机向DSP系统发送的控制数据;(2)上位机向DSP传送的曝光图形格式数据;(3)DSP向上位机传送的标记检测数据。 接口芯片选用Cypress Semiconductor公司的EZ-USB FX2(CY7C68013),具体连接见图2。芯片外接24MHz晶振,可配27~33pF的外接电容,经过内部振荡电路和锁相环(PLL)倍频电路可产生8051的默认工作频率(48MHz),另外它还需要产生 480MHz的时钟脉冲以供收发器使用。当CY7C68013的V CC上电达到3.3V以后,内部的锁相环电路大约需要200μs的时间才能稳定,因此,在芯片的复位引脚RESET端通常外接一个RC网络电路,以提供延迟的低电平有效的复位信号。 CY7C68013通过I2C总线接口外挂串行 EEPROM, I2C接口包括时钟信号线SCL和数据信号线SDA,它们分别是漏极开路输出和磁滞输入,在应用时都必须接2.2kΩ的上拉电阻,即使没有外接I 2C设备,SCL,SDA也要上拉到3.3V。 本系统上电后通过I2C总线将固件从外部 EEPROM存储器中下载到芯片内置的RAM中,在CY7C68013复位后便开始执行这一程序代码。在这种情况下,设备描述符被压缩到固件中,同时状态 5 外部存储器扩展电路设计[3] 本系统选用一片AMD公司的低功耗CMOS工艺的 FLASH ROM――AM29LV800B作为扩展的外部程序存储器。 DSP对FLASH的逻辑控制通过一片CPLD译码产生。 由于TMS320C6713芯片具有专门的同步动态存储器接口,并提供SDRAM所需的所有控制和刷新信号,因此可以实现DSP与SDRAM之间的无缝连接[4]。本系统选用的是MICRON公司的MT48LC4M16A2,存储容量为64Mbit,数据宽度为16位,工作时钟可达125MHz,并具有同步接口和内部流水线结构。 6 标记检测与曝光及束闸控制单元 6.1 标记检测单元 6.2 曝光及束闸控制单元 7 实验与结论 图形发生器系统由多个工作模块组成。而数据缓存、控制逻辑、地址译码等电路通常是由RAM芯片、与非门、触发器、缓冲/驱动器等构成,导致整个系统电路复杂、芯片繁多,特别是硬件的固定使得系统换代升级几乎不可能。因此本系统将这些功能全部集成到一片CPLD芯片中,并采用 Verilog-HDL语言开发了控制程序。 由上位机向DSP传输曝光图形数据时,采用批量传输的方式,以达到较高的传输速率。在整个传输过程中,不需要8051对数据进行处理,所以采用自动打包的方式,数据经过FIFO直接发送给DSP。 随着实时信号处理技术的迅猛发展,高性能通用DSP的处理能力也迅速提高,凭借其强大的处理能力,基于DSP的图形发生器已成为一大设计趋势。本文提出的图形发生器硬件方案能够很好地满足图形数据传输及控制的要求,基于USB总线的高速数据采集系统具有可靠性高、数据不丢失、抗干扰性强、便于数据传输和处理等优点。并且系统具有的灵活可编程控制又使本设计方案具有很强的通用性和扩展性。

| ||||||||||||||||