| 您现在的位置:首页 > 技术资料 |

|

基于NDK的数字电视传输流(TS)网络采集系统

概述 电视发展到今天已经进入数字化的时代了,数字电视系统取代模拟电视系统的一大优势在于实现了信息的数字化。电视节目信息实现数字化,所有的信息可以在数字世界里传播、转换、存储和处理,从而使得广播电视网能够和计算机网络相连接,大大提高了信息处理的能力。 TCP/IP是Internet网络上传输数据 所必需的协议,这种网络通信模式在PC机之间的实现已经完善, 但是由于体积、价格等因素限制了应用的范围。因此,基于TCP/IP 协议与Ethernet的嵌入式系统网络通信设计成为目前一个热门的话题。 本 系统实现了在以TI公司的TMS320DM643为核心的嵌入式系统 中对数字电视传输流信号进行采集与在Ethernet中传输。利用本系统可轻松的实现在局域网中对数字电视传输流信号的传输、调度。数字电视传输流信号源是针对欧洲数字有线广播系统标准(DVB-C)的数字有线电视信号。网 络接入硬件是在以TI公司的TMS320DM643为核心的嵌入式系统中实现,网络接入软件采用了TI公司的针对C6000系列DSP推出的TCP/IP NDK(Network Developer's Kit)网络开发包来实现。

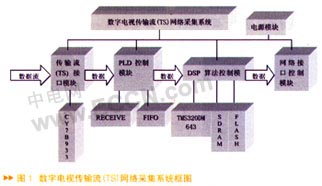

电路部分主要由五部分组成。数字电视传输流网络采集系统框图如图1所示。

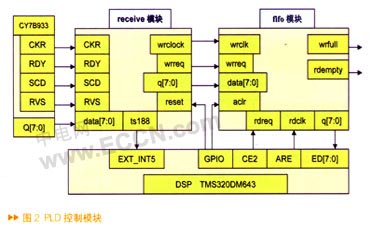

传输流(TS)接口模块 传输流接口模块由CY7B933输入接口芯片及其电器接口电路组成。CY7B933输入接口电路是点对点的传输模块,可以通过光纤、同轴电缆和双绞线进行高速的串行数据传输。输入接口符合DVB-ASI的接口标准。输入接口接收到串行位流后,通过内部PLL时钟同步恢复数据的时钟信息,并对位流进行串并转换、解码和传输检错等操作。这种输入接口能灵活的实现把高速点对点串行数据转变成并行数据,而且应用领域广泛,包括各种服务器,存储器和视频传输的应用。 PLD控制模块 在项目中,此部分硬件选用的是Altera公司的CYCLONE EP1C6Q240C8芯片。

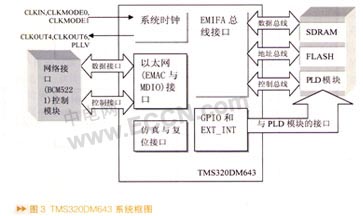

RECEIVE模块的功能是实现与CY7B933接收芯片的接口,把数据从CY7B933接收进来。其工作方式是以一个传输流包为边界接收数据的。 首先RECEIVE模块会检测传输流包的边界,通过查找包头字节(固定为0x47)间的字节数来确定。因为包中数据也可能含有0x47,所以要牺牲三个包的数据来检查三次。当发现0x47这个字节的时候,就会触发一个内部的计数器开始计数。当计数到188后,如果下一个字节又是0x47,说明传输流包属于188个字节的包,那么计数器被清零;如果下一个字节又是0x47,说明传输流包属于188个字节的包,那么计数器被清零,否则计数器清零并重新开始检测边界。 当检测到边界以后,RECEIVE模块开始接收数据包。计数器会从零开始计数,在接收数据的过程中使能wrreq输出有效信号,同时把数据输出到下一级。当计数到188,表示一个数据包接收完成。当一个包的数据接收完之后,计数器清零,并置ts188,保持高电平一个时钟周期。下一个周期检测数据是否为0x47,如果是说明是下一个数据包的边界,否则说明出现了错误,并重新回到上一段所说的检测数据包边界的状态。 此外,PLD模块内会有一个专用计数器记录空包数,当接收到数据包后会首先检测此数据包是否空包,如果是空包PLD模块会把这个空包删除,并在计数器中加一。如果接收的不是空包就会把计数器的值加到这个数据包的私有字段中,并缓存到FIFO。然后计数器自动清零。这样处理数据包的目的是为了减少网络传输的数据流量,从而可以传输更多的传输流数据。把计数器的值加入私有字段是为了在计算机接收到数据后可以把原来的空包恢复出来,从而保证原传输流数据的完整性。 fifo模块 fifo模块的功能实现从RECEIVE模块接收数据,并缓存起来。当RECEIVE模块接收完一个完整的传输流的数据包之后,会发送ts188或TS204的中断信号给DSP,DSP就会启动EDMA功能从fifo模块接收数据。DSP与fifo模块是采用异步连接的方式,具体的接收操作在DSP部分说明中加以描述。 DSP(TMS320DM643)算法处理模块 此模块主要以TI公司的TMS320DM643为核心的嵌入式系统组成。主要实现从PLD模块接收传输流数据包,把数据包打包成TCP/IP格式,并实现对网络接口(BCM5221)控制模块的初始化,然后把数据包传送到网络模块。 为了实现上述功能,必须建立起一套以TMS320DM643为核心的基本系统。系统各个组成部分如图3所示。

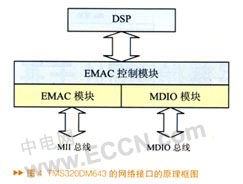

时钟配置:EMIF内核时钟ECLKIN是133MHz。此外,系统上外设总线、EDMA传输和L2存储器的工作时钟为CPU内核时钟的1/2,即300MHz;片上定时器的工作时钟为CPU内核时钟的1/8,即75MHz。 中断配置:TMS320DM643除了RESET和NMI引脚提供外部不可屏蔽中断请求输入以外,还有2个外部中断引脚GP0[5]/EXT_INT5、GP0[7]/EXT_INT7提供可屏蔽的外部中断请求输入。系统中EXT_INT5外部中断用作PLD模块的请求接收数据信号,每当PLD模块接收完一个传输流(TS)包就会发送一个外部中断信号给DSP,通知DSP接收数据。此外,EDMA中断用于当接收完一个包的数据后做后续处理。 系统对EMIF的使用情况: 系统在CE0空间扩展了4 Mx64-bit的S DRAM 存储器( MT48LC4M32BPG) ,用于存储程序与数据。SDRAM的工作时钟由T MS320DM643 的E CLKOUT1 提供,与E MIF 的工作时钟频率相同,本系统中默认为E CLKIN 为其时钟源,即133MH z。 系统在CE1空间扩展了4Mx8-bit的Flash存储器(AM29LV033C)。在对FLASH进行读/写访问前,需要通过EMIF的CE1控制寄存器CE1CTL将CE1空间配置为8-bit异步存储器接口,及读/写时序。 系统在CE2空间扩展了与PLD模块的fifo模块连接的接口。在DSP看来,fifo模块可视为8-bit异步只读存储器。如图2所示,fifo模块的读使能信号rdreq与TMS320DM643的CE2片选信号连接;fifo模块的读时钟信号rdclk,与TMS320DM643的ARE读使能信号连接。 以太网(EMAC与MDIO)接口 TMS320DM643上集成有一个EMAC+MDIO片上外设,EMAC是Ethernet Media Access Controller的缩写,即以太网媒体访问控制器,MDIO是Management Data Input/Output的缩写,即管理数据输入/输出模块。EMAC+MDIO用于为以太网物理层(PHY)器件提供接口,其中EMAC为接口以太网PHY提供数据通路,MDIO为接口以太网PHY提供管理信息通路。以太网接口主要功能如下:符合IEEE 802.3协议;支持传媒无关接口(MII);八个独立的发送与接收通路;同步的10/100Mbit的数据操作;广播及多帧的传送。 TMS320DM643的网络接口的原理框图如图4所示。

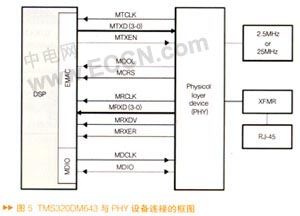

网络接口(BCM5221)控制模块 本系统中用Broadcom公司的BCM5221作为10/100Base-TX以太网收发器,BCM5221的MII接口与TMS320DM643的MII接口对接。具体接口如图5所示。RJ45连接器选用AMP公司的406549-1,其上带两个LED指示灯,右边的LED为绿色,用作指示连接状态。左边的为黄色,正常情况下用来指示数据传输。

系统包括四组电源:系统外接稳压电源,把220V的交流电源电压转换成5V直流电压;PLD模块电源有两种电源供电,分别是3.3V和1.5V;TMS320DM643需要2种电源,分别为CPU核心和周边的I/O接口供电。周边I/O电压要求3.3V,CPU核心电压只要1.4V;网络接口控制模块采用3.3V电源供电。

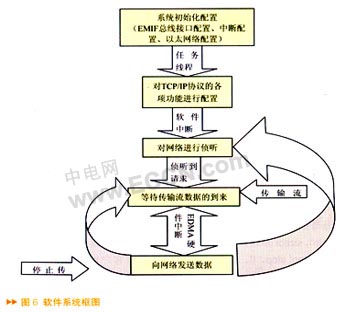

系统的软件设计主要是通过TI公司推出的专门针对C6000系列的TCP/IP网络开发包NDK(Network Developer's Kit)来实现的。该开发包支持TCP/IP协议,并占用较少的系统资源。NDK仅用200~250KB程序空间和95KB数据空间即可支持常规的TCP/IP服务。所以,NDK很适合目前嵌入式系统的硬件环境,是实现DSP网络开发的重要工具。

当客户机的传输请求到来时,系统首先会使GPIO7引脚变为低电平,PLD模块开始发送数据。当其接收到一个完整的传输流数据包后就会发一个中断给DSP,DSP启动EDMA,用ping-pong的方式接收数据进入特定的存储器,当接收完一个完整的传输流数据包后,会产生硬件EDMA中断,中断程序主要是设置特定的标志为1,然后退出硬件中断,重新回到软件中断程序。当软件中断程序检测到特定的标志为1时,就会开始向网络中传输在存储器中的传输流数据包给客户机。当一个数据包传输完毕后,特定的标志会被置0,系统等待下一个数据包的到来。 当客户机要求停止传输的请求到来时,系统会重新使GPIO引脚变为高电平,PLD模块回到初试状态。此时系统也会处于待命状态,继续侦听网络。 系统初始化 初始化配置主要包括了EMIF总线配置、中断配置和底层网络配置三个部分。初始化工作首先在DSP/BIOS的全局参数配置窗口进行设置,然后调用初始化函数进行配置。 在DSP/BIOS的全局配置窗口主要设置了DSP 的工作时钟频率为600MHz,选择使用的片级支持库CSL为 DM642的库,选用小端访问模式,片内256k的SRAM全部用于CACHE高速缓存,并调用初始化函数dm643_init()。 TCP/IP协议配置 初始化程序dm643_init()完成后,从现在起系统将进入各个线程。首先 ,系统会触发任务线程TSK0,在TSK0任务线程中执行函数StackTest(), 其 首先调用NC- SystemOpen()函数完成协议栈及其所需内存的初始 化,然后新件一个系统配置句柄hCfg = CfgNew(),并实现服务器IP地址和网关的配置。在本系统中,IP地 址配 置为“192.168.0.2”;子网掩码为“255.255.255.0”;网关地址为“192.168.0.1”。配置好之后,系统会触发一个软件中断,并做好侦听网络的准备 。 网络侦听 前面在任务线程中已经配置了IP地址和网关,下面就要在软件中断中设置端口和进行侦听。首先在开始使用报路之前,必须分配一个文 件环境fdOpenSession( TaskSelf() )给这个报 路。接着就可以创建一个报路对象stcp = socket(AF_INET, SOCK_STREAM, IPPROTO_TCP),并设置端口sin1.sin_port =htons(1000),在这里我们设置端口号为1000,当然也可以设置其他的端口号。然后把端口号与报路对象绑定bind( stcp, (PSA) &sin1,sizeof(sin1)。最后进入侦听状态listen( stcp, 1)。 数据的接收 当客户端要求传输数据的信号到来后,系统会使GPIO7引脚变为低电平,PLD模块开始发送数据。DSP通过EDMA方式来接收数据。EDMA可以在没有CPU参与的情况下,由EDMA控制器完成DSP存储空间内的数据搬移。系统主要采用EDMA的ping-pong方式来连续的接收数据。用ping-pong的方式的目的是为了使接收操作和发送操作分开处理,争强程序的操作性和可读性。 网络发送 接收完一帧的数据后会触发硬件中断,在硬件中断函数中会把特定的标志置为1,然后从硬件中断函数中返回,并进入软件中断函数。软件中断函数把刚刚接收到的数据发送到网络中。 软件中断函数会一直侦听是否有新的TCP/IP报路连接请求,当检测到有新的报路连接请求,就会创建一个报路来连接到请求连接的应用程序。建立连接后,软件中断函数会等待客户机的命令。客户机此时会发送一个传输命令给服务器,服务器接收到这个命令后,软件中断函数就会准备发送数据。 软件中断函数会等待一帧传输流数据的到来,也就是等待特定的标志置1。当检测到标志位置1后,软件中断函数就会把刚刚接收到的数据包发送出去。发送成功后,又会把标志位置0,重新等待下一个数据包的到来。如此循环的把数据包发送出去。

本系统的硬件和软件功能已经实现,网络传输的速度为2Mbytes/s。按照 此速度,假设传输流中的空包百分比为40%计算,可以传输5 Mbytes/s的传输流数据,也就是50Mbit/s的传输流,至少可以传输2~3路的TS流节目。因此,可以证明本系统的设计方法合理、有效。 DSP(TMS320DM643)在数字信号处理方面具有的比其他芯片更为强大优势,现在我们已经在DSP(TMS320DM643)系统中实现了数字电视传输流的网络功能,日后可以在本系统中继续增添新的数字信号处理,特别是视音频处理模块,从而实现更强大的功能。

| ||||||||||||||||||||